· AtlasPCB Engineering · News · 6 min read

APEX EXPO 2026: AI and Advanced Packaging Reshape Electronics Manufacturing

Key takeaways from APEX EXPO 2026 — AI infrastructure is driving unprecedented demand for HDI and high-layer-count PCBs, while quantum computing and heterogeneous integration open new frontiers.

The Largest Electronics Manufacturing Event in North America Signals a Paradigm Shift

APEX EXPO 2026, organized by the Global Electronics Association (formerly IPC), delivered a resounding message to the electronics industry: artificial intelligence isn’t just a topic of conversation anymore — it’s fundamentally reshaping what the industry builds, how it builds, and the standards it must meet.

The event, held in April 2026, featured four keynote speeches spanning AI’s promise and risks, quantum computing’s leap from laboratory to real-world deployment, the critical role of heterogeneous integration in advanced electronics packaging, and the raw power that electronics manufacturing brings to the global economy. Coverage from iConnect007 highlighted these presentations as among the most forward-looking in the event’s history.

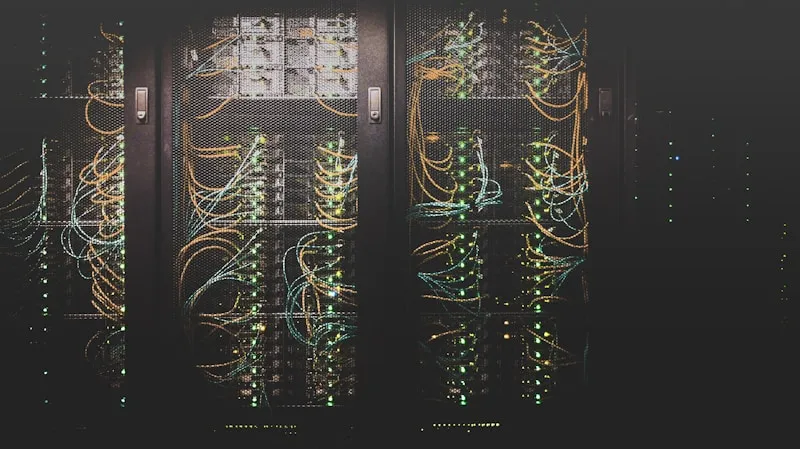

Photo by Headway on Unsplash — Free to use under Unsplash License

AI Infrastructure: The New Driver for Advanced PCBs

Perhaps the most tangible impact on the PCB industry comes from the explosive growth of AI infrastructure. Data centers powering large language models, computer vision systems, and enterprise AI applications require server hardware with PCB specifications that push the boundaries of conventional fabrication:

High layer counts: AI accelerator boards routinely require 20–36 layers, with some next-generation designs pushing beyond 40 layers. These aren’t standard FR-4 production runs — they demand precise impedance control, ultra-tight registration tolerances (±2 mil or better), and materials with controlled dielectric properties.

HDI complexity: High Density Interconnect technology is essential for routing the enormous pin counts of modern AI processors (often exceeding 5,000 BGA pins). HDI stackups with 2-3 stages of sequential lamination, microvias on 100μm pads, and via-in-pad designs have become standard requirements rather than exotic capabilities.

Thermal management: AI chips dissipating 500–1000W require PCBs with advanced thermal management — thick copper planes (2–4 oz), dense thermal via arrays, and embedded heat spreaders. The PCB isn’t just an interconnect substrate; it’s a thermal pathway.

Signal integrity at 56–112 Gbps: PAM4 signaling at 56 Gbps and emerging 112 Gbps SerDes links demand PCB materials with ultra-low loss (Df <0.005 at 10 GHz), controlled fiber weave effects, and meticulous impedance matching per signal integrity best practices.

At the event, exhibitor All4-PCB’s Managing Director Ralph Jacobo reported seeing “strong market momentum in North America driven by increased demand for advanced PCB manufacturing technologies,” with particular emphasis on investments in multilayer lamination capabilities spurred by AI infrastructure needs.

Quantum Computing: From Lab to Cafeteria

One of the most striking presentations came from IBM’s David Lokken-Toyli, principal research scientist at IBM Quantum, who described the installation of a quantum computer in the middle of a public cafeteria at Cleveland Clinic. This vivid image — a cutting-edge quantum system operating in an everyday environment — encapsulates a turning point for the technology.

Lokken-Toyli emphasized that getting quantum computing from the lab to the real world depends not just on physicists, but on an electronics supply chain ready to support entirely new system requirements. Quantum computing systems present unique challenges for PCB manufacturers:

- Cryogenic operation: Quantum processors operate at temperatures near absolute zero (15 millikelvin), requiring interconnect substrates that maintain integrity through extreme thermal cycling from room temperature to cryogenic conditions

- Ultra-low noise: Signal paths to and from qubits must maintain extraordinarily low electromagnetic noise, placing extreme demands on shielding, grounding, and EMC design practices

- New interconnect architectures: The interface between cryogenic quantum hardware and room-temperature classical control electronics requires novel PCB and cable solutions

While quantum computing PCB volumes are small today, the technology’s trajectory suggests growing demand for specialized high-reliability boards that meet these unique requirements.

Advanced Packaging: Where Integration Actually Happens

The event’s emphasis on heterogeneous integration and advanced electronics packaging (AEP) reflects a broader industry truth: the most significant performance gains increasingly come from how different technologies are combined at the package and substrate level, not from improvements in any single component.

Chiplet architectures — where multiple specialized die are combined in a single package using 2.5D or 3D integration — are driving demand for:

- Ultra-fine-trace substrates with line/space below 25/25 μm

- Package-to-PCB integration with via pitches matching BGA ball grids at 0.4–0.65mm

- Mixed-material stackups combining organic substrates with silicon or glass interposers

- Embedded die technology incorporating active ICs within substrate layers

This convergence of packaging and PCB technology means that PCB fabricators must increasingly think like package substrate manufacturers — working with tighter tolerances, finer features, and more exotic materials than traditional board shops have historically handled.

Standards Development: Keeping Pace with Technology

Behind the keynotes, hundreds of volunteers worked in APEX EXPO meeting rooms on IPC standards development committees. These quiet sessions — less glamorous than the exhibition floor but equally important — are updating standards documents to keep pace with rapidly evolving manufacturing technology:

- IPC-6012F revision addressing HDI blind via reliability requirements

- IPC-2226 updates for HDI design guidelines with sub-75μm via structures

- New IPC-2231 work on embedded component test and qualification methods

- IPC-6018 revisions for high-frequency material characterization

The Global Electronics Association’s CEO John Mitchell noted that adapting standards for AI applications, workforce development challenges, and sustainability requirements are top priorities for the organization going forward.

What This Means for PCB Designers and Buyers

APEX EXPO 2026 painted a clear picture: the PCB industry is being pulled upward in complexity by AI infrastructure demand, while simultaneously being pushed toward new frontiers by quantum computing and advanced packaging. For design engineers, this means:

- Invest in HDI design skills — multi-stage HDI with advanced stackup design is becoming the baseline for high-performance applications

- Understand your fabricator’s capabilities — not all PCB manufacturers can deliver the layer counts, tolerances, and materials required for AI hardware

- Design for manufacturability — as designs push boundaries, close collaboration with your fabrication partner during the design phase prevents costly iterations

- Stay current with standards — IPC standards revisions directly impact design rules and acceptance criteria

Atlas PCB at the Forefront

Atlas PCB continues to invest in advanced manufacturing capabilities aligned with the trends highlighted at APEX EXPO 2026. Our facility supports high-layer-count boards up to 68 layers, HDI with up to 3-stage sequential lamination, and a range of high-performance materials from Rogers, Isola, Panasonic, and AGC. As AI infrastructure, quantum systems, and advanced packaging drive increasingly complex PCB requirements, we’re here to help you navigate the technical challenges.

Working on an AI hardware or advanced packaging project? Get a quote with a free engineering review, or talk to our HDI specialists about your design requirements.

- news

- apex-expo

- ai

- advanced-packaging

- electronics-manufacturing