· AtlasPCB Engineering · Engineering · 18 min read

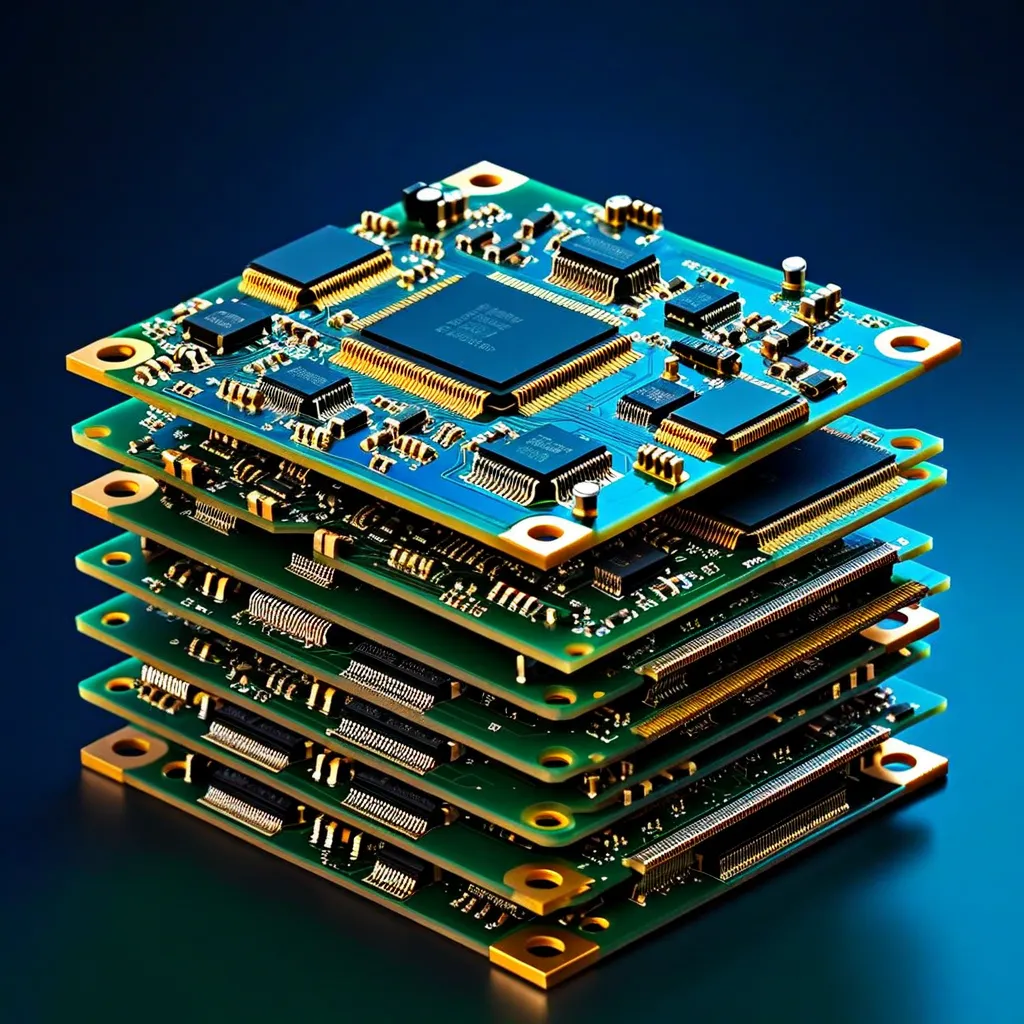

PCB电源完整性与去耦设计:高速数字系统PDN设计完全指南

深入掌握电源分配网络设计方法,包括目标阻抗计算、去耦电容选型策略、PDN谐振分析,以及面向FPGA和SoC的PDN仿真验证技术。

PCB电源完整性与去耦设计:完整PDN设计指南

电源完整性(PI)已成为现代高速PCB中最关键的设计挑战。随着核心电压降至1.0V以下而先进FPGA和SoC的瞬态电流超过50A,电源分配网络(PDN)必须以毫欧级阻抗在DC到数GHz的频率范围内提供稳定、低噪声的电源。设计不良的PDN不仅会导致电源轨噪声——还会产生同步开关噪声(SSN),降低信号完整性,增加误码率,甚至使一个原本合理的设计无法工作。

本指南涵盖完整的PDN设计方法论:目标阻抗计算、去耦电容网络设计、电源平面优化、PDN谐振分析和基于仿真的验证。

理解电源分配网络

PDN是从电压调节模块(VRM)输出到IC电源引脚的完整电气路径,包括:

- 电压调节模块(VRM):提供稳压直流电压,具有有限的输出阻抗和带宽(通常有效至10-50kHz)

- 体积电容:VRM附近的10-470μF电解或聚合物电容,有效频段

1kHz到1MHz - 中频去耦电容:分布在板上的100nF-1μF MLCC电容,有效频段

1MHz到100MHz - 高频去耦电容:直接放置在IC电源引脚处的1nF-100nF MLCC电容,有效频段

100MHz到1GHz - 电源/地平面对:提供分布式平面电容的PCB铜平面,500MHz以上有效

- 过孔互连:平面和电容焊盘之间的垂直连接

- IC封装:键合线/凸点和内部电源分配的寄生电感

每个元素在特定频段主导PDN阻抗。设计挑战在于确保这些频段之间平滑、低阻抗过渡,不出现超过目标阻抗的谐振峰值。

目标阻抗:PDN设计的基础

目标阻抗公式

目标阻抗定义了任何频率下PDN允许的最大阻抗:

Z_target = ΔV / ΔI

其中:

- ΔV = 允许电压纹波 = V_supply × 纹波百分比

- ΔI = 最大瞬态电流需求

实例计算:Xilinx Kintex UltraScale FPGA

以Kintex UltraScale XCKU115为例:

VCCINT(0.95V核心):

- 纹波容限:±3% → ΔV = 0.95V × 0.03 = 28.5mV

- 最大瞬态电流:25A

- Z_target = 28.5mV / 25A = 1.14mΩ

VCCO(1.8V I/O Bank):

- 纹波容限:±5% → ΔV = 1.8V × 0.05 = 90mV

- 最大瞬态电流:8A

- Z_target = 90mV / 8A = 11.25mΩ

VCCAUX(1.8V辅助):

- 纹波容限:±5% → ΔV = 1.8V × 0.05 = 90mV

- 最大瞬态电流:3A

- Z_target = 90mV / 3A = 30mΩ

VCCINT的1.14mΩ目标极具挑战性——这驱动了对紧密间距平面对、大量去耦网络和精细过孔设计的需求。因此,高性能的多层PCB叠层设计对电源完整性至关重要。

频率范围考虑

目标阻抗必须从DC满足到最高关注频率:

f_max = 1 / (π × t_rise)

对于上升时间100ps的信号:f_max = 1 / (π × 100ps) = 3.18 GHz

这意味着PDN阻抗必须从DC到3GHz以上保持在Z_target以下——跨越近10个十倍频程。

去耦电容网络设计

三级去耦策略

有效的去耦需要协调的电容网络,每级针对特定频段优化:

第一级——体积去耦(DC到~1MHz):

- 容值:10μF到470μF

- 类型:聚合物铝、钽聚合物或高容值MLCC

- 数量:每个电源轨2-6个

- 放置:靠近VRM输出,25mm以内

- 用途:提供持续电流需求的充电储备,弥合VRM带宽限制

第二级——中频去耦(1MHz到~200MHz):

- 容值:100nF到1μF

- 类型:X7R或X5R MLCC,0402或0201封装

- 数量:每个主要电源轨10-40个

- 放置:分布在IC占位区域,距电源引脚10mm以内

- 用途:为中频瞬态提供电荷,填补体积电容和高频电容之间的阻抗空白

第三级——高频去耦(200MHz到~2GHz):

- 容值:1nF到100nF

- 类型:C0G/NP0 MLCC以获得最低ESR,0201或01005封装

- 数量:每个主要电源轨20-80+个

- 放置:直接在IC电源引脚处,2mm以内,同层或紧邻过孔

- 用途:在需求点抑制高频开关噪声

电容自谐振频率(SRF)

每个实际电容都有一个从容性转变为感性行为的自谐振频率:

SRF = 1 / (2π × √(L_ESL × C))

SRF以下,电容按预期工作。SRF以上,它表现为电感,去耦无效。这就是为什么需要多种电容值——它们的SRF交错排列,在整个频谱上提供连续的低阻抗。

常见MLCC封装的典型SRF:

| 容值 | 封装 | ESL (pH) | SRF (MHz) |

|---|---|---|---|

| 100μF | 1210 | 900 | 0.5 |

| 10μF | 0805 | 700 | 1.9 |

| 1μF | 0402 | 450 | 7.5 |

| 100nF | 0402 | 450 | 24 |

| 100nF | 0201 | 250 | 32 |

| 10nF | 0201 | 250 | 100 |

| 1nF | 0201 | 250 | 318 |

反谐振:PDN的隐形杀手

当两个不同SRF的电容并联时,会在它们各自SRF之间的频率产生反谐振峰值。在反谐振处,阻抗可能远超目标阻抗,可能导致电源轨振荡。

缓解策略:

- 使用大量相同值的电容(并联降低ESR/ESL,不产生新的反谐振)

- 选择SRF间隔不超过一个十倍频程的电容值

- 在体积电容上串联阻尼电阻(0.5-2Ω)

- 通过PDN仿真验证——永远不要仅凭经验法则设计

电源平面设计与优化

紧密间距平面对:最佳高频去耦

500MHz以上,由于安装电感的影响,离散电容的效果越来越差。电源/地平面对本身通过分布式平面电容成为主要的去耦机制。

平面对的电容为:

C_plane = ε₀ × εr × A / d

IPC-2141设计指南: 为获得最佳高频PDN性能,使用≤100μm(4mil)介质间距的电源/地平面对。针对1GHz以上低于2mΩ阻抗的高端设计应使用50μm(2mil)甚至25μm(1mil)间距。

| 介质厚度 | 电容(FR-4,100cm²) | 1GHz阻抗 |

|---|---|---|

| 200μm(8mil) | 1.86nF | ~85mΩ |

| 100μm(4mil) | 3.72nF | ~43mΩ |

| 50μm(2mil) | 7.44nF | ~21mΩ |

| 25μm(1mil) | 14.88nF | ~11mΩ |

这就是为什么高级叠层设计将电源/地平面对放在相邻层上并使用最薄的可用半固化片——这是实现500MHz以上低PDN阻抗最有效的方法。

载流能力:IPC-2152合规

电源平面必须在不过度温升的情况下承载大量直流和交流电流。IPC-2152取代了较旧的IPC-2221图表,采用更精确的热模型。

IPC-2152内层平面关键参数:

| 电流(A) | 10°C温升最小铜宽(1oz) | 20°C温升最小铜宽(1oz) |

|---|---|---|

| 5 | 2.0mm | 1.2mm |

| 10 | 6.5mm | 3.8mm |

| 20 | 18mm | 10.5mm |

| 30 | 35mm | 20mm |

对于高电流轨道(>10A),考虑在电源平面上使用2oz铜厚。铜厚与电流能力之间的关系不是线性的——同等温升下,铜厚加倍仅使电流能力增加约40%。

电压降计算:

V_drop = I × R_sheet × L / W

其中R_sheet为方块电阻(1oz铜在25°C时为0.49mΩ/sq,85°C时升至约0.64mΩ/sq)。对于1.0V电源轨通过1oz铜50mm长30mm有效宽度承载20A:

V_drop = 20A × 0.49mΩ × (50/30) = 16.3mV(1.63%)

这已消耗±3%预算的相当部分,为交流纹波留下极少的余量。

过孔设计与电源分配

过孔载流能力

根据IPC-2221,单个镀通孔(0.3mm钻孔,25μm镀层)在10°C温升下可承载约1.5A。高电流电源连接需要多个过孔:

| 所需电流 | 最少过孔数(0.3mm,25μm镀层) |

|---|---|

| 5A | 4 |

| 10A | 7 |

| 20A | 14 |

| 30A | 20 |

过孔电感与PDN影响

每个过孔都为PDN路径增加寄生电感。典型通孔过孔(0.3mm钻孔,1.6mm板厚)约有0.5-1.0nH电感。通过两个过孔(电源+地)连接的去耦电容,总增加电感为1-2nH。

在100MHz时,1nH电感产生的阻抗为: Z_L = 2π × 100MHz × 1nH = 0.63Ω

这比典型2mΩ目标阻抗高出几个数量级!这就是高频去耦电容的放置和过孔设计至关重要的原因。

降低过孔电感的策略:

- 每个电容焊盘使用多个过孔(每焊盘2-3个过孔可降低50-67%的电感)

- 最小化过孔长度——使用盲/埋孔连接内层平面。了解更多关于过孔类型及其应用

- 将电容焊盘直接放置在盘中孔连接上

- 在BGA扇出区域使用铜填充盘中孔

- 保持电源/地过孔对的紧密间距(≤1mm)

电源平面过孔缝合

过孔缝合连接不同层上的电源平面并防止平面对之间的腔体谐振。根据IPC-2141指南:

缝合过孔间距 ≤ 最高关注频率处的λ/20

对于f_max = 3GHz的FR-4(εr = 4.2): λ = c / (f × √εr) = 3×10⁸ / (3×10⁹ × √4.2) = 48.8mm

最大缝合过孔间距 = 48.8mm / 20 = 2.44mm

实际中,多GHz设计标准为2-3mm缝合过孔间距。对于具有微过孔的HDI PCB,甚至可以实现1-1.5mm的更紧密间距,并推荐用于最苛刻的PDN应用。

腔体谐振与缓解

腔体谐振的成因

平行电源/地平面对形成谐振腔——本质上是矩形波导。谐振频率为:

f_mn = (c / 2√εr) × √((m/L)² + (n/W)²)

对于FR-4中100mm × 80mm平面对:

- f_10 = 732MHz(沿长度方向第一模式)

- f_01 = 915MHz(沿宽度方向第一模式)

- f_11 = 1.17GHz(对角模式)

在这些谐振频率处,PDN阻抗急剧上升,通常超过目标阻抗10-100倍。

腔体谐振缓解方法

1. 平面周边过孔缝合: 沿板边和开口周围以≤λ/20间距放置接地过孔,提高基频并降低Q因子。

2. 嵌入式平面电容: 超薄介质层(25-50μm)将谐振峰推至更高频率,在该处被介质和导体损耗自然衰减。

3. 腔体内短路过孔: 跨平面区域的缝合过孔网格破坏谐振模式,对大面积无中断平面区域最为有效。

4. 有损介质材料: 较高Df材料(Df > 0.015)提供自然谐振阻尼,尽管这与信号完整性对低损耗材料的趋势相矛盾。

面向FPGA和SoC的多轨PDN设计

现代FPGA如Xilinx Versal或Intel Agilex有10-20+个独立电源轨:

| 轨道类型 | 典型电压 | 最大电流 | Z_target | 优先级 |

|---|---|---|---|---|

| 核心逻辑 | 0.70-0.88V | 30-80A | 0.5-1.5mΩ | 关键 |

| I/O Bank | 1.2-3.3V | 5-15A | 5-20mΩ | 高 |

| 收发器 | 0.9-1.1V | 3-10A | 3-10mΩ | 关键 |

| 辅助 | 1.8V | 2-5A | 15-40mΩ | 中 |

| 配置 | 1.8/2.5V | 0.5-2A | 30-80mΩ | 低 |

多轨PDN设计层次

- 为最关键的轨道分配专用平面对(核心、收发器),使用最薄可用介质

- 使用平面分割共享较低电流轨道,边界处放置缝合电容

- 将VRM放置在靠近FPGA处——最小化电力传输路径长度

- 按FPGA厂商要求的顺序上电(通常先核心,然后I/O,最后辅助)

- 独立和联合仿真每个轨道以捕获轨道间耦合效应

PDN仿真与验证

频域分析

PDN仿真工具计算特定探测点(通常是IC电源引脚)的阻抗与频率关系。主要输出是Z(f)图——阻抗幅值与频率——必须在整个频段内保持在Z_target以下。

行业标准工具:

- ANSYS SIwave:全波3D电磁求解器,PDN分析的黄金标准

- Keysight ADS (PathWave):电路与EM联合仿真

- Cadence Sigrity PowerDC/PowerSI:与Allegro PCB流程集成

- Altium PDN Analyzer:内置于Altium Designer

测量验证

制板后的PDN验证使用双端口VNA测量:

- 将端口1连接到IC附近的电源过孔

- 将端口2连接到端口1旁边的接地过孔

- 测量S21并转换为阻抗:Z = 2 × Z0 × 10^(S21_dB/20)

实用设计规则总结

| 参数 | 设计规则 | 参考标准 |

|---|---|---|

| 目标阻抗 | Z = ΔV/ΔI,从DC到f_max保持平坦 | — |

| 电源/地间距 | ≤100μm(4mil),优选≤50μm(2mil) | IPC-2141 |

| 过孔缝合间距 | f_max处≤λ/20 | IPC-2141 |

| 去耦电容放置 | 高频电容距IC电源引脚≤2mm | IPC-2141 |

| 电源过孔电流 | ~1.5A每过孔(0.3mm,25μm,10°C温升) | IPC-2152 |

| 平面铜厚 | <10A用≥1oz,>10A用≥2oz | IPC-2152 |

| 接地平面 | 连续不分割,专用层 | IPC-2141 |

常见PDN设计错误

- 仅使用单一电容值:在VRM带宽和电容SRF之间产生反谐振峰

- 忽略过孔电感:每个过孔连接即使1nH也会使高频电容失效

- 去耦电容放置距IC过远:每毫米增加约1nH走线电感

- 分割接地平面:破坏回流路径连续性,参见PCB接地技术

- 高电流轨道铜厚不足:导致DC电压降侵蚀纹波预算

- 跳过PDN仿真:经验法则设计无法可靠达到毫欧级阻抗目标

- 忽视热管理:高电流VRM和平面区域产生显著热量

结论

电源完整性不是事后考虑——它是必须从初始叠层定义到最终布局验证全程关注的基本设计约束。关键原则很直接:计算目标阻抗,设计覆盖全频段的协调去耦网络,使用紧密间距电源/地平面对获得高频性能,并在制板前通过仿真验证一切。

在Atlas PCB,我们常规制造具有50μm介质电源平面对、BGA去耦盘中孔以及同时优化信号和电源完整性的受控阻抗叠层的电路板。我们的工程团队可以在您完成布局之前审查您的设计并提供PDN建议。

准备好开始您的项目了吗? 上传您的Gerber文件获取免费工程审查,或联系工程师讨论您的设计需求。

- power-integrity

- decoupling

- pdn-design

- signal-integrity